Application Note (AN-EP71xx-1)

# RAIL SEQUENCING IN EP71XX INTEGRATED VOLTAGE REGULATORS

AN-EP71xx-1

EMPOWER SEMICONDUCTOR, INC. FEBRUARY 2024

## **1.** Table of Contents

| 2. | Sum   | nn  | nary                                                                                            | 3  |

|----|-------|-----|-------------------------------------------------------------------------------------------------|----|

| 3. | Intr  | 00  | duction                                                                                         | 3  |

| 4. | Pro   | gr  | amming Power Up/Down Sequencing                                                                 | 4  |

|    | 4.1   |     | User-Programmable Registers for Sequencing                                                      | 4  |

|    | 4.2   |     | Enabling or Disabling of VR Rails                                                               | 6  |

|    | 4.2.2 | 1   | Scenario 1: Enabling/disabling VR through I <sup>2</sup> C                                      | 6  |

|    | 4.2.2 | 2   | Scenario 2: Enabling/disabling VR using GPIO as Hardware Enable                                 | 8  |

|    | 4.2.3 | 3   | Scenario 3: Enabling/disabling VR through I <sup>2</sup> C with start/hold conditions and delay | 10 |

|    | 4.2.4 | 4   | Scenario 4: Enabling/disabling VR using GPIO as HW Enable with start/hold conditions and delay  | 14 |

|    | 4.3   |     | Relative Rail Sequencing                                                                        | 17 |

|    | 4.3.2 | 1   | Sequential rail sequencing                                                                      | 17 |

|    | 4.3.2 | 2   | Simultaneous rail sequencing                                                                    | 18 |

|    | 4.3.3 | 3   | Ratiometric rail sequencing                                                                     | 18 |

| 5. | Con   | ncl | lusion                                                                                          | 19 |

| 6. | Арр   | be  | ndix                                                                                            | 20 |

|    | 6.1   |     | Detailed Description of User-Programmable Registers in EP71xx                                   | 20 |

|    | 6.1.2 | 1   | VR Enable Registers                                                                             | 20 |

|    | 6.1.2 | 2   | VR MTP Enable Registers                                                                         | 20 |

|    | 6.1.3 | 3   | GPIO Functions Register                                                                         | 21 |

|    | 6.1.4 | 4   | VR Power Sequencing                                                                             | 24 |

|    | 6.1.5 | 5   | VR Output Voltage Regulators                                                                    | 28 |

|    | 6.1.6 | 6   | VR Control Registers                                                                            | 29 |

|    | 6.2   |     | Multi-time Programming                                                                          | 31 |

| 7. | Rev   | isi | ion History                                                                                     | 32 |

## **Programming Rail Sequencing in EP71xx IVRs**

## 2. Summary

Empower Semiconductor's EP71xx series is a family of Step-Down Integrated voltage regulators (IVRs) available in single to quad-output configurations. The EP71xx IVRs offer capability to customize and program output voltage, soft-start times, and power up/down sequencing for each of the outputs independently. This application note will explain how to achieve the desired power up/down sequencing by programming the user-configurable registers, through various examples.

The EP71xx Product Description and Datasheet provide more details on the ratings, electrical characteristics, operating characteristics, and functional features of the product family.

## 3. Introduction

Many complex systems in the industry use FPGAs, microprocessors, DSPs etc., all usually requiring different rail voltages to power the memory, core, auxiliary outputs, and input/outputs (I/Os). Furthermore, these require stringent power up and down sequencing of the rails.

Power sequencing is the order of the startup and shutdown of the various rails within the system executed in a controlled manner with defined time intervals and dependencies between each rail. To prevent high inrush currents, prevent latch-ups, and to ensure reliable and correct operation, sequencing of the multiple rails is crucial and is an important aspect of the overall system design. Improper sequencing of the rails can cause incorrect operation or even damage the system. FPGA vendors such as Xilinx specify either a recommended or required power-up/down sequence in their datasheets. In addition, timing requirements such as soft-start ramp rates and delays are also listed in the datasheets. In most cases, the recommended power-down sequence is the reverse order of the power-up sequence but the EP71xx is flexible enough to accommodate any order needed.

The EP71xx family features the ability to prototype the sequencing the multiple outputs through software and program the target sequence in the device through MTP (multi-time programmable) memory. This enables 'default' power-up sequencing in the production system, removing the need for a system micro-controller to control or program the sequence. More information about MTP option can be found in the product datasheet or the MTP programming app note.

## 4. **Programming Power Up/Down Sequencing**

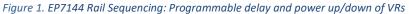

The EP71xx features digitally controllable power-up/down sequencing allowing the user to program the order and delay times of the startup and shutdown of the various voltage regulator rails (VRs). Figure 1 show an example of a programmed sequence using EP7144.

<u>Note</u>: EP7144 is a quad-output IVR in the EP71xx series and is used for discussion in this document.

#### 4.1 User-Programmable Registers for Sequencing

<u>Table 1</u> lists the user-programmable registers to program power-sequencing including delays, GPIO functions, VR output voltages, and soft-start ramp rates. Each of these registers is further explained in this <u>Section 6.1</u>.

During early design/prototype phases, these registers can be used to perform trial runs on sequences either using the EP71xx Demo Board and associated GUI or on an application-specific system board with an on-board controller. For production, the register values determined to suit the application can subsequently be programmed into the MTP memory to provide the default power-up.

| Register Name                                                           | Bits  | Reg Address |            |            |            |  |

|-------------------------------------------------------------------------|-------|-------------|------------|------------|------------|--|

| (User-programmable registers)                                           | BITS  | <u>VR1</u>  | <u>VR2</u> | <u>VR3</u> | <u>VR4</u> |  |

| VRn_ENABLE - <u>Table 12</u>                                            | [3:0] |             | 0x20       |            |            |  |

| GPIO0_FUNCTIONS - Table 13                                              | [6:0] | 0x23        |            |            |            |  |

| GPIO1_FUNCTIONS - Table 13                                              | [6:0] | 0x24        |            |            |            |  |

| VRn_POWERSEQUENCE - <u>Table 14</u> , <u>Table 15</u> , <u>Table 16</u> | [7:0] | 0x25        | 0x27       | 0x29       | 0x2B       |  |

| VRn_DELAY - <u>Table 14</u> , <u>Table 18</u>                           | [7:0] | 0x26        | 0x28       | 0x2A       | 0x2C       |  |

| VPp DAC TARGET Table 19                                                 | [9:8] | 0x41        | 0x51       | 0x61       | 0x71       |  |

| VRn_DAC_TARGET - <u>Table 19</u>                                        | [7:0] | 0x42        | 0x52       | 0x62       | 0x72       |  |

| VRn_CNTRL - <u>Table 20</u>                                             | [7:0] | 0x45        | 0x55       | 0x65       | 0x75       |  |

#### Table 1: User-Programmable Registers table

In <u>Figure 1</u>, the output voltage of each rail is programmed to a different voltage setting. This is set through VRn\_DAC\_TARGET registers. In addition, the soft-start rates can be programmed for each rail independently through VRn\_SOFT\_START\_RATE register bit-fields in VRn\_CNTRL register.

VRn\_START\_CONDITION and VRn\_HOLD\_CONDITION register bit-fields in VRn\_POWERSEQUENCE can be used to define any dependency and order between the individual VR rails during power-up/down. Delay times for the startup and shutdown of the various rails can be programmed through Register VRn\_DELAY.

EP71xx has two general purpose input/output pins (GPIO1, GPIO2) that can be configured to perform functions such as 'Hardware Enable', 'Alternate Power-Good output', 'Alerts output' and 'DVS input' through the registers **GPIO0\_FUNCTIONS, GPIO1\_FUNCTIONS.** In this application note, GPIOx configured as a hardware enable is discussed.

The following sections explain the power up/down sequencing through examples.

### 4.2 Enabling or Disabling of VR Rails

The EP71xx's individual VR rails can be enabled or disabled in four different ways as listed below.

It is important to note that the device EN pin (chip enable) should always stay high to keep the VRs enabled. If the EN pin goes low, all rails will shut down irrespective of the programmed power-down sequence.

- 1. <u>Standard I<sup>2</sup>C command (software enable)</u>: A VRn can be enabled by writing to the VRn\_ENABLE registers through an I<sup>2</sup>C command (where, n = 1 to 4, VRn represent each of the VR rails in the EP71xx device).

- 2. <u>GPIO0/1 setting (hardware enable)</u>: GPIOx can be configured as a hardware enable pin to power up one or all the rails. Setting GPIOx high turns on the rail while setting GPIOx low will disable the specified rail.

In many systems, a micro-controller or similar device is unavailable to coordinate sequencing, and the main system processor needs its core powered up prior to its IO functions being available. Hence, a method for initiating a sequence through hardware is required. This can be accomplished using GPIOx in EP71xx.

<u>Note</u>: When a GPIOx pin is configured as HW Enable for a VRn, the corresponding **VRn\_ENABLE** register bit is not set to 1. The **VRn\_ENABLE** bits and the HW Enable functions are logically OR'ed. The VRn can be disabled only by pulling the GPIO voltage low or by setting chip EN pin to low.

Start/hold conditions defined to depend on another VR: A rail can be powered up based on another VR rail being enabled and in regulation, or the rail can be powered down based on another VR being disabled. A timing associated with the dependent VRn condition can also be programmed for both enable or disable delay.

<u>Note</u>: When a rail is enabled through a start condition, its corresponding **VRn\_ENABLE** register bit is not set to 1. The VRn can be disabled only through a stop condition associated with any other VRn status (refer to example in Figure 5) or by setting the chip EN pin to low.

4. <u>MTP Enable register</u>: The MTP\_VRn\_ENABLE register is available for programming through MTP to force a VR to be enabled as soon as EN is pulled high. For more information on this, refer to the datasheet and the MTP programming app note.

In most FPGA vendor datasheets, the recommended or required power-up sequence is in the order of: Core voltage  $(0.85V/0.9V) \rightarrow Auxiliary supply (1V/1.2V) \rightarrow I/O$  supplies (1.8V)

Hence, these voltage rails and power-up/down sequence have been used in the examples in this application note. The power-down sequence is typically the reverse order of the power-up sequence.

<u>Scenario 1</u> and <u>Scenario 2</u> describe enabling and disabling of VR through I<sup>2</sup>C and GPIO respectively.

<u>Scenario 3</u> and <u>Scenario 4</u> explain power-up/down sequences with start/hold conditions and delays applied to the individual rails.

#### 4.2.1 Scenario 1: Enabling/disabling VR through I<sup>2</sup>C

In <u>Figure 2</u>, VR1, VR3, VR4 of EP7144 are all enabled individually by writing to each **VRn\_ENABLE** register through the  $I^2C$  bus. No programmable delays have been set in this case. After issuing the 'Execute' command, each VR is enabled with the minimum default delay of 40 $\mu$ s.

#### To disable the VRs, set VR1\_ENABLE, VR3\_ENABLE and VR4\_ENABLE to zero through the I<sup>2</sup>C bus.

Loads all registers as shown in <u>Table 3</u> to achieve this power-up sequence.

Figure 2. Enabling rails VR1, VR3, VR4 through I<sup>2</sup>C with no delays

| Channel #        | Waveform<br>Name     | Waveform details Details            |                                                     | Measured delay  |

|------------------|----------------------|-------------------------------------|-----------------------------------------------------|-----------------|

| CH2<br>(magenta) | I <sup>2</sup> C_SCL | SCL waveform of<br>I <sup>2</sup> C | I <sup>2</sup> C command to enable VR1,<br>VR3, VR4 | -               |

| CH1              | VR1_VOUT             | Output Voltage of                   | Set to 0.8V.                                        | No programmable |

| (yellow)         |                      | VR1                                 | Enable VR1 through I <sup>2</sup> C                 | delay added     |

| CH3              | VR3_VOUT             | Output Voltage of                   | Set to 1V.                                          | No programmable |

| (blue)           |                      | VR3                                 | Enable VR3 through I <sup>2</sup> C                 | delay added     |

| CH4              | VR4_VOUT             | Output Voltage of                   | Set to 1.8V.                                        | No programmable |

| (green)          |                      | VR4                                 | Enable VR4 through I <sup>2</sup> C                 | delay added     |

Table 2: Waveform description for Figure 2

| Bit field Name      | Register Address | Bits  | Reg Setting<br>(hex) | Description of changes                     |

|---------------------|------------------|-------|----------------------|--------------------------------------------|

| VR1_DAC_TARGET      | 0x41             | [9:8] | 0x148                | Sets VR1 Output Voltage to                 |

|                     | 0x42             | [7:0] | 0.12                 | 0.8V                                       |

| VR3_DAC_TARGET      | 0x61             | [9:8] | 0x19A                | Sets VR3 Output Voltage to 1V              |

|                     | 0x62             | [7:0] |                      |                                            |

| VR4_DAC_TARGET      | 0x71             | [9:8] | 0x2E2                | Sets VR4 Output Voltage to                 |

|                     | 0x72             | [7:0] |                      | 1.8V                                       |

| VR1_ENABLE          |                  | [0]   | 1                    | Enable VR1                                 |

| VR3_ENABLE          | 0x20             | [1]   | 1                    | Enable VR3                                 |

| VR4_ENABLE          |                  | [2]   | 1                    | Enable VR4                                 |

| VR1_DELAY_UP        |                  | [7]   | 0                    |                                            |

| VR1_DELAY_DOWN      | 0x25             | [6]   | 0                    | No start/hold conditions,                  |

| VR1_START_CONDITION |                  | [5:3] | 0x00                 | default settings                           |

| VR1_HOLD_CONDITION  |                  | [2:0] | 0x00                 |                                            |

| VR1_DELAY           | 0x26             | [7:0] | 0x00                 | No delay, default settings                 |

| VR3_DELAY_UP        |                  | [7]   | 0                    |                                            |

| VR3_DELAY_DOWN      | 0x29             | [6]   | 0                    | No start/hold conditions,                  |

| VR3_START_CONDITION |                  | [5:3] | 0x00                 | default settings                           |

| VR3_HOLD_CONDITION  |                  | [2:0] | 0x00                 |                                            |

| VR3_DELAY           | 0x2A             | [7:0] | 0x00                 | No delay, default settings                 |

| VR4_DELAY_UP        |                  | [7]   | 0                    |                                            |

| VR4_DELAY_DOWN      | 0x2B             | [6]   | 0                    | No start/hold conditions,                  |

| VR4_START_CONDITION | 0/20             | [5:3] | 0x00                 | default settings                           |

| VR4_HOLD_CONDITION  |                  | [2:0] | 0x00                 |                                            |

| VR4_DELAY           | 0x2C             | [7:0] | 0x00                 | No delay, default settings                 |

| EXECUTE             | 0x0F             | [7:0] |                      | Write any value to apply register settings |

Table 3: Register settings for Figure 2

#### 4.2.2 Scenario 2: Enabling/disabling VR using GPIO as Hardware Enable

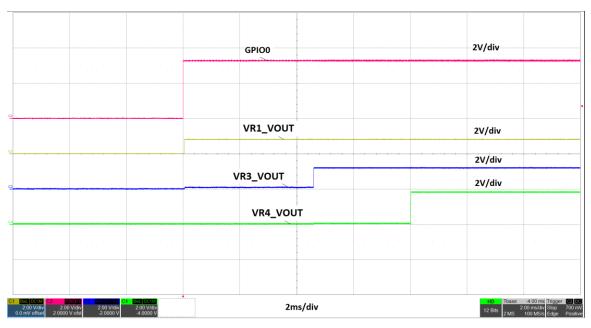

In Figure 3, GPIO0 is programmed as HW Enable for VR1, VR3, VR4. No programmable delays have been set in this case, and no start/hold conditions between VRs have been included. The 'Execute' command is issued. When GPIO0

is set HI, the rails VR1, VR3, VR4 power-up with the minimum default delay of 40µs. The rails power-down when GPIO0 goes low.

Table 5 shows the register settings to achieve this power-up sequence described in scenario 2.

<u>Note</u>: When GPIOx is configured as HW Enable for a VRn, the corresponding **VRn\_ENABLE** register bit is not set to 1. The VRn can be disabled only by pulling the GPIO voltage low, or by setting chip EN pin to low.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | GPIO0    | 2V/div                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          | <br>                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | VR1_VOUT | 1V/div                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | VR3_VOUT | <br>1V/div                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | VR4_VOUT | 2V/div                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          |                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          |                                                                               |

| Dot M         C2         Evel oct M         C3         Evel oct M         C4         Evel oct M           1.00 V/div         2.00 V/div         1.00 V/div         2.00 V/div         2.00 V/div         2.00 V/div         0.0 V/div         2.00 V/div         -0.00 V/div         -0.000 V         -6.0000 V | 2 | ms/div   | HD Tbase -2.00 ms Trigger C<br>2.00 ms/div Stop 1.2<br>2 MS 100 MS/s Edge Pos |

Figure 3. Hardware-enable of VR1, VR3, VR4 through GPIOO (configured as enable for VR1, VR3, VR4) with no delays

| Channel #              | Channel # Waveform Waveform details |                | Details                                                             | Measured delay  |

|------------------------|-------------------------------------|----------------|---------------------------------------------------------------------|-----------------|

| CH2<br>(magenta) GPIO0 |                                     | GPIO0 voltage  | GPIO0 is set to function as 'Hardware<br>Enable' for VR1, VR3, VR4. | -               |

| CH1                    | VR1_VOUT                            | Output Voltage | Set to 0.8V.                                                        | No programmable |

| (yellow)               |                                     | of VR1         | Enabled through GPIO0                                               | delay added     |

|                        |                                     | Output Voltage | Set to 1V.                                                          | No programmable |

|                        |                                     | of VR3         | Enabled through GPIO0                                               | delay added     |

| CH4                    | VR4_VOUT                            | Output Voltage | Set to 1.8V.                                                        | No programmable |

| (green)                |                                     | of VR4         | Enabled through GPIO0                                               | delay added     |

#### Table 4: Waveform description Figure 3

| Bit field Name | Register Address | Bits  | Reg Setting<br>(hex) | Description of changes |

|----------------|------------------|-------|----------------------|------------------------|

| VR1_DAC_TARGET | 0x41             | [9:8] | 0x148                |                        |

Empower Semiconductor, Inc.

|                     | 0x42 | [7:0] |       | Sets VR1 Output Voltage to<br>0.8V         |

|---------------------|------|-------|-------|--------------------------------------------|

| VR3_DAC_TARGET      | 0x61 | [9:8] | 0x19A | Sets VR3 Output Voltage to 1V              |

| VIS_DAC_TARGET      | 0x62 | [7:0] |       | Sets VNS Output Voltage to 1V              |

| VR4_DAC_TARGET      | 0x71 | [9:8] | 0x2E2 | Sets VR4 Output Voltage to                 |

|                     | 0x72 | [7:0] | UXZEZ | 1.8V                                       |

| VR1_ENABLE          |      | [0]   | 0     | Default settings                           |

| VR3_ENABLE          | 0x20 | [1]   | 0     | Default settings                           |

| VR4_ENABLE          |      | [2]   | 0     | Default settings                           |

| GPIO0_FUNCTION      |      | [6:4] | 0x04  | GPIO0 set as HW Enable                     |

| GPIO0_VRS           | 0x23 | [3:0] | 0x0D  | GPIO0 set HW EN for VR1, VR3,<br>VR4       |

| VR1_DELAY_UP        |      | [7]   | 0     |                                            |

| VR1_DELAY_DOWN      | 0x25 | [6]   | 0     | No start/hold conditions,                  |

| VR1_START_CONDITION |      | [5:3] | 0x00  | default settings                           |

| VR1_HOLD_CONDITION  |      | [2:0] | 0x00  |                                            |

| VR1_DELAY           | 0x26 | [7:0] | 0x00  | No delay, default settings                 |

| VR3_DELAY_UP        |      | [7]   | 0     |                                            |

| VR3_DELAY_DOWN      | 0x29 | [6]   | 0     | No start/hold conditions,                  |

| VR3_START_CONDITION | 0,25 | [5:3] | 0x00  | default settings                           |

| VR3_HOLD_CONDITION  |      | [2:0] | 0x00  |                                            |

| VR3_DELAY           | 0x2A | [7:0] | 0x00  | No delay, default settings                 |

| VR4_DELAY_UP        |      | [7]   | 0     |                                            |

| VR4_DELAY_DOWN      | 0x2B | [6]   | 0     | No start/hold conditions,                  |

| VR4_START_CONDITION | UNED | [5:3] | 0x00  | default settings                           |

| VR4_HOLD_CONDITION  |      | [2:0] | 0x00  |                                            |

| VR4_DELAY           | 0x2C | [7:0] | 0x00  | No delay, default settings                 |

| EXECUTE             | 0x0F | [7:0] |       | Write any value to apply register settings |

Table 5: Register settings for Figure 3

#### 4.2.3 Scenario 3: Enabling/disabling VR through I<sup>2</sup>C with start/hold conditions and delay

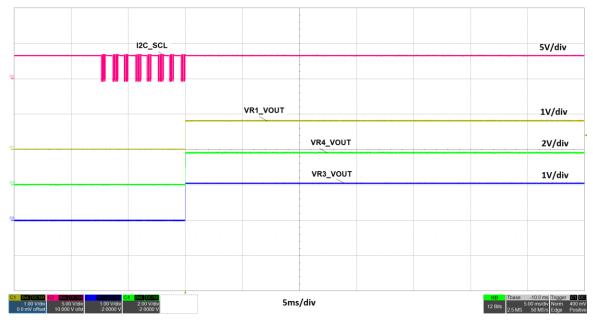

Figure 4 and Figure 5 show the power-up and power-down of three rails with start/hold conditions and programmable delays. The sequence in this case is controlled directly through I<sup>2</sup>C commands and not through GPIOs.

For the sequences described in scenario 3, load registers as shown in Table 8.

During power-up, Rail VR1 is enabled through the I<sup>2</sup>C command (VR1\_ENABLE = 1). Rail VR3 and Rail VR4 are enabled through start conditions with delays – VR3 power-up depends on VR1 power-up and VR4 depends on VR3.

<u>Note</u>: When a rail is enabled through a start condition, its corresponding **VRn\_ENABLE** register bit is not set to 1. In this case, VR3\_ENABLE and VR4\_ENABLE are not set to 1. The VRn can be disabled only through a stop condition associated with any other VRn status (refer to example in <u>Figure 5</u>) or by setting the chip EN pin to low.

Figure 4. Enabling VR1 through I<sup>2</sup>C, power-up of VR3, VR4 with start conditions and programmable delays

| Channel #        | Waveform<br>Name     | Waveform<br>details                 | Details                                                                                                                                        | Measured delay                       |

|------------------|----------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| CH2<br>(magenta) | I <sup>2</sup> C_SCL | SCL waveform<br>of I <sup>2</sup> C | I <sup>2</sup> C command to enable VR1                                                                                                         | -                                    |

| CH1<br>(yellow)  | VR1_VOUT             | Output Voltage<br>of VR1            | Set to 0.8V.<br>Enable VR1 through I <sup>2</sup> C                                                                                            | No programmable<br>delay added       |

| CH3<br>(blue)    | VR3_VOUT             | Output Voltage<br>of VR3            | Set to 1.2V.<br>Rail VR3 is dependent on VR1 through start<br>condition; it powers-up after rail VR1 is<br>enabled and has reached regulation. | Measured delay =<br>2.84ms from VR1. |

| CH4<br>(green)   | VR4_VOUT             | Output Voltage<br>of VR4            | Set to 1.8V.<br>Rail VR4 powers-up after rail VR3 is enabled<br>and has reached regulation; defined through<br>start condition                 | Measured delay =<br>4.66ms from VR3. |

Table 6: Waveform description Figure 4

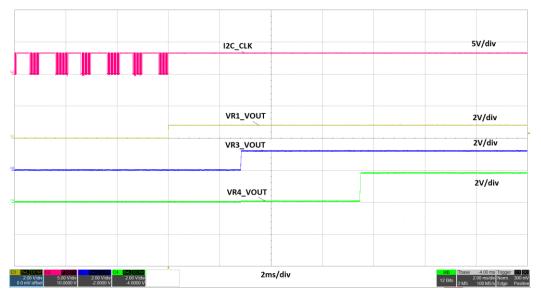

Power-down sequence is the reverse of the power-up sequence. An  $I^2C$  command is issued to disable VR1 (VR1\_ENABLE = 0) which initiates a shutdown request. As VR1 has a hold condition dependent on VR3 which in turn depends on VR4 through the hold condition, VR1 continues to stay high. VR4 powers down first as it has no hold conditions, followed by VR3 and finally VR1.

Figure 5. Disabling VR1 through I<sup>2</sup>C, power-down of VR3, VR4 with hold conditions and programmable delays

| Channel #        | Waveform<br>Name                                                                                                | Waveform<br>details      | Details                                                                                                                                               | Measured delay                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| CH2<br>(magenta) | a) I <sup>2</sup> C_SCL SCL waveform I <sup>2</sup> C command to disable VR1 (this initiates shutdown sequence) |                          | -                                                                                                                                                     |                                                             |

| CH1<br>(yellow)  | VR1_VOUT                                                                                                        | Output Voltage<br>of VR1 | Rail VR1 will hold the rail ON as long as<br>VR3 is active defined through hold<br>condition. VR1 will shut down only after<br>rail VR3 has shutdown. | Measured delay =<br>2.73ms from VR3.                        |

| CH3<br>(blue)    | VR3_VOUT                                                                                                        | Output Voltage<br>of VR3 | Rail VR3 will hold the rail ON as long as<br>VR4 is active defined through hold<br>condition. VR3 will shut down only after<br>rail VR4 has shutdown. | Measured delay =<br>2.73ms from VR4.                        |

| CH4<br>(green)   | VR4_VOUT                                                                                                        | Output Voltage<br>of VR4 | Rail VR4 disables first in the sequence.<br>Set VR1_ENABLE = 0 through I <sup>2</sup> C<br>command.                                                   | Measured delay =<br>4.7ms from I <sup>2</sup> C<br>command. |

Table 7: Waveform description Figure 5

Empower Semiconductor, Inc.

Application Note (AN-EP71xx-1)

| Bit field Name          | Register<br>Address | Bits  | Reg Setting<br>(hex) | Description of changes                                                                                           |

|-------------------------|---------------------|-------|----------------------|------------------------------------------------------------------------------------------------------------------|

|                         | 0x41                | [9:8] | 0x148                | Sets VR1 Output Voltage to 0.8V                                                                                  |

| VR1_DAC_TARGET          | 0x42                | [7:0] | 08146                | Sets VR1 Output Voltage to 0.8V                                                                                  |

| VR3_DAC_TARGET          | 0x61                | [9:8] | 0x1EC                | Sets VR3 Output Voltage to 1.2V                                                                                  |

| VIG_DAC_TARGET          | 0x62                | [7:0] | UXILC                | Sets VNS Output Voltage to 1.2V                                                                                  |

| VR4_DAC_TARGET          | 0x71                | [9:8] | 0x2E2                | Sets VR4 Output Voltage to 1.8V                                                                                  |

|                         | 0x72                | [7:0] | UNZEZ                | Sets Vite Output Voltage to 1.5V                                                                                 |

| VR1_ENABLE              |                     | [0]   | 1                    | Enable VR1 (for power-up sequence)                                                                               |

| VR3_ENABLE              | 0x20                | [1]   | 0                    | Default settings                                                                                                 |

| VR4_ENABLE              |                     | [2]   | 0                    | Default settings                                                                                                 |

| VR1_DELAY_UP            |                     | [7]   | 0                    | - No delay during power-up                                                                                       |

| VR1_DELAY_DOWN          |                     | [6]   | 1                    | - Delay applied during power-down                                                                                |

| VR1_START_CONDITION     | 0x25                | [5:3] | 0x00                 | - No start condition                                                                                             |

| VR1_HOLD_CONDITION      |                     | [2:0] | 0x02                 | - Shut down of Rail VR1 dependent on<br>shutdown of Rail VR3                                                     |

| VR1_DELAY               | 0x26                | [7:0] | 0x3C                 | Sets delay time                                                                                                  |

| VR3_DELAY_UP            |                     | [7]   | 1                    | - Delay applied during power-up and                                                                              |

| VR3_DELAY_DOWN          |                     | [6]   | 1                    | power-down - Startup of Rail VR3 dependent on startup                                                            |

| VR3_START_CONDITION     | 0x29                | [5:3] | 0x01                 | of Rail VR1                                                                                                      |

| VR3_HOLD_CONDITION      |                     | [2:0] | 0x04                 | - Shutdown of Rail VR3 depends on<br>shutdown of Rail VR4                                                        |

| VR3_DELAY               | 0x2A                | [7:0] | 0x3C                 | Sets delay time                                                                                                  |

| VR4_DELAY_UP            |                     | [7]   | 1                    | Delay applied during power-up and power-                                                                         |

| VR4_DELAY_DOWN          |                     | [6]   | 1                    | down                                                                                                             |

| VR4_START_CONDITION     | 0x2B                | [5:3] | 0x04                 | - Startup of Rail VR4 dependent on startup<br>of Rail VR3                                                        |

| VR4_HOLD_CONDITION      |                     | [2:0] | 0x00                 | <ul> <li>No hold condition. Shutdown of Rail VR4<br/>depends on I<sup>2</sup>C command VR1_ENABLE = 0</li> </ul> |

| VR4_DELAY               | 0x2C                | [7:0] | 0x64                 | Sets delay time                                                                                                  |

| EXECUTE                 | 0x0F                | [7:0] |                      | Write any value to register to apply register settings                                                           |

| For power-down sequence | е                   |       |                      |                                                                                                                  |

| VR1_ENABLE              | 0x20                | [0]   | 0                    | Disable VR1 (for power-down sequence)                                                                            |

| EXECUTE                                              | 0x0F | [7:0] | Write any value to apply register settings |  |  |  |  |

|------------------------------------------------------|------|-------|--------------------------------------------|--|--|--|--|

| Table 8: Register settings for Figure 4 and Figure 5 |      |       |                                            |  |  |  |  |

4.2.4 Scenario 4: Enabling/disabling VR using GPIO as HW Enable with start/hold conditions and delay

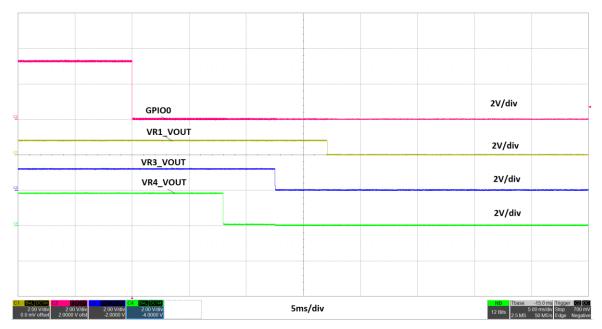

In Figure 6 and Figure 7: Power-up/down sequence with GPIO0 set as HW Enable for rail VR1.

Setting GPIO0 as high initiates the power-up sequence. VR3 and VR4 are powered-up through start conditions; VR3 depends on VR1 startup and VR4 depends on VR3 startup.

Figure 6. Enable of VR1 through GPIOO, power-up of VR3, VR4 through start conditions and with programmable delays

| Channel #        | Waveform<br>Name | Waveform Details details |                                                                                                                                                       | Measured delay                      |

|------------------|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| CH2<br>(magenta) | GPIO0            | GPIO0 voltage            | GPIO0 is set to function as 'Hardware<br>Enable' for VR1. Set high.                                                                                   | -                                   |

| CH1<br>(yellow)  | VR1_VOUT         | Output<br>Voltage of VR1 | Set to 0.8V. Enabled using GPIO0 HW<br>Enable.                                                                                                        | No programmable<br>delay added      |

| CH3<br>(blue)    | VR3_VOUT         | Output<br>Voltage of VR3 | Set to 1.2V.<br>Rail VR3 depends on VR1 through start<br>condition; it will power-up only after rail<br>VR1 is enabled and has reached<br>regulation. | Measured delay =<br>4.6ms from VR1. |

| CH4<br>(green) | VR4_VOUT | Output<br>Voltage of VR4 | Set to 1.8V.<br>Rail VR4 will power-up only after rail VR3<br>is enabled and has reached regulation;<br>defined through start condition | Measured delay =<br>8ms from VR3. |

|----------------|----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|----------------|----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

#### Table 9: Waveform description Figure 6

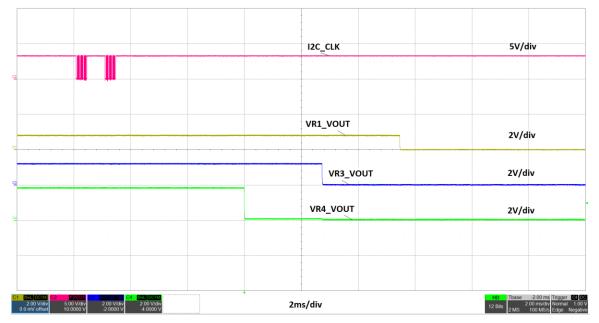

Figure 7. GPIO0 configured as HW-enable for rails VR1: here, GPIO0 is disabled and rails power-down with programmable delays and hold conditions

When GPIO0 is configured as HW Enable for a VR1, the corresponding **VR1\_ENABLE** register bit is not set to 1. Powerdown sequence starts when GPIO0 voltage is pulled low. VR1 will not power-down first as it has a hold condition dependent on VR3 rail. The shutdown request causes VR4 to power-down first as it has no dependencies. VR3 powers down based on the hold and delay conditions followed by VR1 powering down.

| Channel #        | Waveform<br>Name | Waveform<br>details      | Details                                                                                   | Measured delay                      |

|------------------|------------------|--------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|

| CH2<br>(magenta) | GPIO0            | GPIO0 voltage            | -                                                                                         |                                     |

| CH1<br>(yellow)  | VR1_VOUT         | Output<br>Voltage of VR1 | Rail VR1 shuts down only after rail<br>VR3 shuts down; defined through<br>hold condition. | Measured delay = 4.6ms<br>from VR3. |

| CH3 (blue)       | VR3_VOUT         | Output<br>Voltage of VR3 | Rail VR3 shuts down only after rail<br>VR4 has shutdown, defined in hold<br>condition.    | Measured delay = 4.5ms<br>from VR4. |

| CH4<br>(green) | VR4_VOUT | Output<br>Voltage of VR4 | Rail VR4 disables when GPIO0 is pulled low. | Measured delay = 8ms<br>from GPIO0 Disable. |

|----------------|----------|--------------------------|---------------------------------------------|---------------------------------------------|

|                |          | Table 10:                | Waveform description Figure 7               |                                             |

| Bit field Name      | Register Address | Bits  | Reg Setting<br>(hex) | Description of changes                                       |

|---------------------|------------------|-------|----------------------|--------------------------------------------------------------|

| VR1_DAC_TARGET      | 0x41             | [9:8] | 0x148                | Sets VR1 Output Voltage to 0.8V                              |

|                     | 0x42             | [7:0] | 0/140                |                                                              |

| VR3_DAC_TARGET      | 0x61             | [9:8] | 0x1EC                | Sets VR3 Output Voltage to 1.2V                              |

|                     | 0x62             | [7:0] |                      |                                                              |

| VR4_DAC_TARGET      | 0x71             | [9:8] | 0x2E2                | Sets VR4 Output Voltage to 1.8V                              |

|                     | 0x72             | [7:0] | ONLLL                |                                                              |

| VR1_ENABLE          |                  | [0]   | 0                    | Default settings                                             |

| VR3_ENABLE          | 0x20             | [1]   | 0                    | Default settings                                             |

| VR4_ENABLE          |                  | [2]   | 0                    | Default settings                                             |

| GPIO0_FUNCTION      | 0x23             | [6:4] | 0x04                 | GPIO0 set as HW Enable                                       |

| GPIO0_VRS           | 0/20             | [3:0] | 0x01                 | GPIO0 set HW EN for VR1                                      |

| VR1_DELAY_UP        |                  | [7]   | 0                    | - No delay during power-up                                   |

| VR1_DELAY_DOWN      | 0x25             | [6]   | 1                    | - Delay applied during power-down                            |

| VR1_START_CONDITION |                  | [5:3] | 0x00                 | - No start condition                                         |

| VR1_HOLD_CONDITION  |                  | [2:0] | 0x02                 | - Shut down of Rail VR1 dependent on<br>shutdown of Rail VR3 |

| VR1_DELAY           | 0x26             | [7:0] | 0x64                 | Sets delay time                                              |

| VR3_DELAY_UP        |                  | [7]   | 1                    | - Delay applied during power-up and power-down               |

| VR3_DELAY_DOWN      |                  | [6]   | 1                    | - Startup of Rail VR3 dependent on                           |

| VR3_START_CONDITION | 0x29             | [5:3] | 0x01                 | startup of Rail VR1                                          |

| VR3_HOLD_CONDITION  |                  | [2:0] | 0x04                 | - Shut down of Rail VR3 dependent on shutdown of Rail VR4    |

| VR3_DELAY           | 0x2A             | [7:0] | 0x64                 | Sets delay time                                              |

| VR4_DELAY_UP        |                  | [7]   | 1                    | Delay applied during power-up and                            |

| VR4_DELAY_DOWN      | 0x2B             | [6]   | 1                    | power-down                                                   |

| VR4_START_CONDITION | 0,20             | [5:3] | 0x04                 | - Startup of Rail VR4 dependent on                           |

| VR4_HOLD_CONDITION  |                  | [2:0] | 0x00                 | startup of Rail VR3                                          |

|           |      |       |      | <ul> <li>No hold condition. Shut down of Rail</li> <li>VR4 dependent on GPIO0 disable.</li> <li>(GPIO0 set low).</li> </ul> |

|-----------|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------|

| VR4_DELAY | 0x2C | [7:0] | 0xAF | Sets delay time                                                                                                             |

| EXECUTE   | 0x0F | [7:0] |      | Write any value to the register to apply register settings                                                                  |

Table 11: Register settings for Figure 6 and Figure 7

## 4.3 Relative Rail Sequencing

Most FPGAs have requirements on voltage ramp-up time for rails to prevent excess inrush current and ensure correct operation. A power-supply with adjustable soft-start ramp rates is usually preferred in FPGA applications.

There are typically three common types of multi-rail sequencing (discussed below). The EP71xx series can support all these rail sequencing methods.

#### 4.3.1 Sequential rail sequencing

In this method, one supply rail is turned on first, followed by a set delay before the next rail is turned on. Examples of this method were discussed <u>Section 4.2</u>.

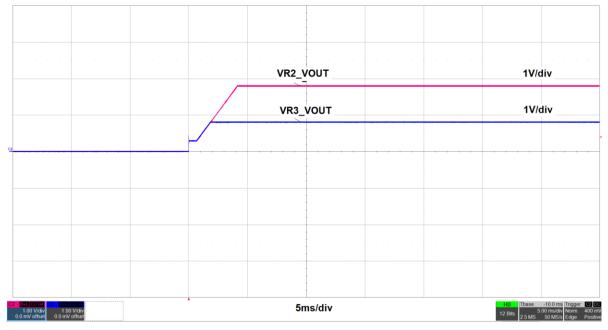

Figure 8 shows an example of sequential rail sequencing. Rails VR2 and VR3 are ramping up at the same soft-start rate. Rail VR2 ramp-up is followed by a fixed delay before rail VR3 ramps up. A consistent soft-start rate for different rails (dV/dt) enables a consistent and manageable inrush current.

Figure 8. Sequential sequencing of rails VR2 and VR3 with same soft-start ramp rates, VR2 powers-up with delay

#### 4.3.2 Simultaneous rail sequencing

In this method, voltage rails ramp-up together at the same soft-start ramp rate. The core voltage which is the lower voltage reaches its final value before the higher voltage rail (aux, I/O type of rails) has reached its final value.

Figure 9 shows an example of simultaneous rail sequencing. Rails VR2 and VR3 start ramping up at the same time at the same soft-start rate.

Figure 9. Simultaneous sequencing of rails VR2 and VR3 with same soft-start rates and with no delay

#### 4.3.3 Ratiometric rail sequencing

In this method, the rails start-up at the same time and reach their final voltage levels at the same time. This requires the soft-start ramp rates to be set proportional to the rail voltage to achieve regulation at the same time.

Figure 10 shows an example of simultaneous rail sequencing. Rails VR2 and VR3 start ramping up at the same time at different soft-start rates.

|  | <br> |       |          |        |

|--|------|-------|----------|--------|

|  |      |       | VR2_VOUT | 1V/div |

|  |      | -     |          | 1V/div |

|  |      | -     |          |        |

|  |      | <br>- |          |        |

|  |      | -     |          |        |

|  |      |       |          |        |

|  |      | -     |          |        |

|  |      |       |          |        |

|  | <br> |       |          |        |

|  |      | -     |          |        |

Figure 10. Ratiometric sequencing of rails VR2 and VR3, powering-up with different soft start ramp rates

## 5. Conclusion

This application note provides details on how the EP71xx family of integrated voltage regulators can address the sequencing requirements of multiple-rail applications in various industry applications.

The highly programmable features of these IVRs can help the user easily customize to their system needs to ensure overall reliable operation.

## 6. Appendix

## 6.1 Detailed Description of User-Programmable Registers in EP71xx

#### 6.1.1 VR Enable Registers

EP71xx offers capability to enable each of the output rail (VR) independently through VRn\_ENABLE.

| Reg<br>Address | Bits  | Bit Field Name | Read/<br>Write | Reset Value | Description                                             |

|----------------|-------|----------------|----------------|-------------|---------------------------------------------------------|

|                | [7:4] | -              | -              | -           | Not used                                                |

|                | 3     | VR4_ENABLE     |                | 0x00        |                                                         |

| 0x20           | 2     | VR3_ENABLE     | R/W            | 0x00        | VR enable input:<br>Write a 1 to VRn_EN to turn on VRn. |

|                | 1     | VR2_ENABLE     | r, vv          | 0x00        | Write a 0 to VRn_EN to turn off VRn.                    |

|                | 0     | VR1_ENABLE     |                | 0x00        | _                                                       |

Table 12: VR Enable Register

#### 6.1.2 VR MTP Enable Registers

| Reg<br>Address | Bits                  | Bit Field Name | Read/<br>Write | Reset<br>Value                                                                                                     | Description                                                  |  |

|----------------|-----------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

|                | 3                     | MTP_VR4_ENABLE |                | 0x00                                                                                                               | Program this register through MTP (multi-time programming)to |  |

| 0v21           | 2                     | MTP_VR3_ENABLE |                | 0x00                                                                                                               | force enable VRn by default as soon as chip EN is high       |  |

| 0.21           | 0x21 1 MTP_VR2_ENABLE | R/W            | 0x00           | The new programmed value will take into effect when the device goes through a power cycle (toggle of chip EN pin). |                                                              |  |

|                | 0                     | MTP_VR1_ENABLE |                | 0x00                                                                                                               | device goes through a power cycle (toggle of thip EN phil).  |  |

#### 6.1.3 GPIO Functions Register

EP71xx provides two General Purpose Input/Output pins (GPIO0, GPIO1) that can be configured for various functions through the **GPIOx\_FUNCTION** registers for selected VR rails defined through the **GPIOx\_VRs** registers (listed in **Table 13**).

- **Hardware Enable**: GPIO can be configured as a HW Enable pin for the VRs indicated in the **GPIO\_VRs** register.

Note:

- It is possible to configure GPIO0 and GPIO1 as HW enables for one rail. In this case, either of the GPIO pins can start the rail.

- The VR that has been enabled will power up with a default delay of typically 80µs. Additional delay can be included in the startup of the VR through the delay register bits (Table 14).

- When a GPIO is configured to act as HW Enable for a VRn, the corresponding VRn\_ENABLE register bit (Table 12) is not set to 1. The VRn can be disabled only by pulling the GPIO voltage low or by disabling the device (Chip Enable is disabled or PVIN is pulled low).

| Reg     |                     |                | Read/ | Reset          |                                                     |                  | Fu               | nction/Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------------------|----------------|-------|----------------|-----------------------------------------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address | Bits                | Bit Field Name | Write | Value<br>(hex) | GPIO<br>Setting                                     | FUNCTION         | Input/<br>Output | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | [7]                 | -              | -     | -              | -                                                   | -                | -                | Not used                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | [6:4] GPIO0_FUNCTIO |                |       |                | 000                                                 | DVS<br>Function  | Input            | This bitfield allows the user to set GPIOO as an<br>input for DVS Function. The logic state of the GPIO<br>pin is fed to the DVSIN signals of each VR included<br>in GPIO_VRS (If a GPIO_VRS bit is configured for<br>both GPIOO and GPIO1, GPIOO takes precedence).<br>The LOW state selects the voltage programmed in<br>VRn_DAC_TARGET register and the HIGH state<br>selects the voltage programmed in<br>VRn_DAC_TARGET2 register. |

| 0x23    |                     | GPIO0_FUNCTION |       | 0x00           | 001                                                 | Alt PG           | Output           | GPIO programmed to function as Power Good.<br>GPIO asserts high when all VRs included in<br>GPIO_VRS are in regulation and output voltage has<br>stabilized.                                                                                                                                                                                                                                                                            |

|         |                     |                | R/W   |                | 010                                                 | GPIO Alert       | Output           | This bitfield allows the GPIOx pins to be used as an output for alert functions for the VRs included in GPIO_VRS. Alert functions for these VRs will cause the GPIO to assert high.                                                                                                                                                                                                                                                     |

|         |                     |                |       |                | 1xx                                                 | HW Enable        | Input            | Bit 6 sets GPIO as an input to serve as a HW enable<br>for the VRs indicated by GPIO_VRS. It can be<br>configured as a HW Enable for one or all of the VRs.                                                                                                                                                                                                                                                                             |

|         |                     |                |       |                | GPIO0 Functions apply to VR4 (Bit 3 is set for VR4) |                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | [3:0]               |                |       |                | GPIO0 Func                                          | tions apply to V | VR3 (Bit 2 is    | s set for VR3)                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | [5.0]               | GPIO0_VRS      |       |                | GPIO0 Func                                          | tions apply to V | VR2 (Bit 1 is    | s set for VR2)                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |                     |                |       |                | GPIO0 Func                                          | tions apply to V | VR1 (LSB is      | set for VR1)                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reg<br>Address | Bits                      | Bit Field Name | Read/<br>Write | Reset<br>Value<br>(hex) | Function/<br>Descriptio<br>n | Reg<br>Address                                                                                                                                                                                                                                                                                                                                                                                                                          | Bits          | Bit Field Name                                                                                                                                                                      |

|----------------|---------------------------|----------------|----------------|-------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | [7]                       | -              | -              | -                       | -                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                       | -             | Not used                                                                                                                                                                            |

|                | 0x24 [6:4] GPIO1_FUNCTION |                |                | 000 DVS<br>Function     | Input                        | This bitfield allows the user to set GPIOO as an<br>input for DVS Function. The logic state of the GPIO<br>pin is fed to the DVSIN signals of each VR included<br>in GPIO_VRS (If a GPIO_VRS bit is configured for<br>both GPIOO and GPIO1, GPIOO takes precedence).<br>The LOW state selects the voltage programmed in<br>VRn_DAC_TARGET register and the HIGH state<br>selects the voltage programmed in<br>VRn_DAC_TARGET2 register. |               |                                                                                                                                                                                     |

| 0x24           |                           | GPIO1_FUNCTION | R/W            | 0x00                    | 001                          | Alt PG                                                                                                                                                                                                                                                                                                                                                                                                                                  | Output        | GPIO programmed to function as Power Good.<br>GPIO asserts high when all VRs included in<br>GPIO_VRS are in regulation and output voltage has<br>stabilized.                        |

|                |                           |                |                |                         | 010                          | GPIO Alert                                                                                                                                                                                                                                                                                                                                                                                                                              | Output        | This bitfield allows the GPIOx pins to be used as an output for alert functions for the VRs included in GPIO_VRS. Alert functions for these VRs will cause the GPIO to assert high. |

|                |                           |                |                |                         | 1хх                          | HW Enable                                                                                                                                                                                                                                                                                                                                                                                                                               | Input         | Bit 6 sets GPIO as an input to serve as a HW enable<br>for the VRs indicated by GPIO_VRS. It can be<br>configured as a HW Enable for one or all of the VRs.                         |

|                |                           |                |                |                         | GPIO0 Funct                  | tions apply to V                                                                                                                                                                                                                                                                                                                                                                                                                        | VR4 (Bit 3 is | s set for VR4)                                                                                                                                                                      |

|                | [3:0]                     | GPIO1_VRS      |                |                         | GPIO0 Funct                  | tions apply to V                                                                                                                                                                                                                                                                                                                                                                                                                        | VR3 (Bit 2 is | s set for VR3)                                                                                                                                                                      |

|                |                           |                |                |                         | GPIO0 Funct                  | tions apply to V                                                                                                                                                                                                                                                                                                                                                                                                                        | VR2 (Bit 1 is | s set for VR2)                                                                                                                                                                      |

|  |  |  |  | GPIO0 Functions apply to VR1 (LSB is set for VR1) |

|--|--|--|--|---------------------------------------------------|

|--|--|--|--|---------------------------------------------------|

Table 13: GPIO Functions Register

#### 6.1.4 VR Power Sequencing

EP71xx offers programmable rail sequencing through which the user can program the order and delay times of the startup and shutdown of the various rails.

| Reg Address                                       | Bits  | Bit Field Name      | Read/Write | Reset Value | Description                                                                                                                   |

|---------------------------------------------------|-------|---------------------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------|

|                                                   | 7     | VRn_DELAY_UP        |            | 0x00        | 1 = VRn will be enabled after the time delay defined in VRn_DELAY.<br>0 = The delay defined in VRn_DELAY will not be applied. |